降压变换器

此條目需要补充更多来源。 (2016年9月11日) |

降压变换器(Buck Converter,又称為Buck变换器),又称為降壓斬波器(Buck Chopper),是會降低電壓的直流-直流轉換器,輸出(負載)端的電壓會比輸入(電源)端要低,但其輸出電流會大於輸入電流。降压变换器是开关电源,一般至少會有二個半導體元件(二極體及電晶體,不過新型的降压变换器可能會用電晶體配合同步整流代替二極體)及至少一個儲能元件(電容器、電感器或是二者都有)。一般也會在輸出端及輸入端加上以電容器為主的濾波器(有時也會配合電感器)以降低電壓漣波[1]。

像降压变换器之類的开关电源其效率會比線性電壓調節器要好,線性穩壓器的電路較簡單,可以降低電壓,且其輸出電壓的漣波會比降压变换器要小很多,但不要的能量會以熱的方式釋放,而且不能提高電流[2]。

降压变换器的效率一般會高過90%,因此常用來將電腦中的主電源(多半是12V)降壓到USB、DRAM及CPU需要的電源(1.8V或更低)。

動作原理

[编辑]

降压变换器的動作原理是其電感器上的電流由二個開關(多半是電晶體及二極體)控制。理想降压变换器會假設其所有的元件都是理想的。其開關及二極體沒有壓降,不導通時不會有漏電流,且電感器沒有等效的串連電阻。而且在同一週期內,假設輸入電壓及輸出電壓都不會變化(因此假設輸出電容為無限大)。

概念

[编辑]降压变换器的概念可用電感器的電壓及電流之間的關係來描述。

一開始開關不導通,電路的電流為零。當開關初次導通時,其電流會增加,電抗器兩端也會因為電流的增加而產生電壓,抵抗電流的增加。此電壓會抵消部份電源端的電壓,因此負載端的電壓會較電源端要低。隨著時間增加,電流的變化率變小,因此電感器的端電壓也變小,使負載端的電壓慢慢上昇,此時電感器中會以磁場方式儲存能量。

若再使開關不導通,電源端的電壓和電路分離,因此電流會下降。由于電流下降,電感器兩端也會產生電壓,抵消電流的下降,此時電感器可視為一電壓源。而在進行儲能和釋能轉換時,電感的正負極會發生變化。電感器利用磁場中儲存的能量使電流流到負載端。此時是由電感器提供電能給電路中的其他元件。若在電感器的電放完之前,開關又再度導通,負載端的電壓就會恆大於零。

連續模式(CCM)

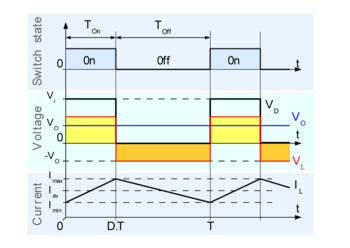

[编辑]若降压变换器在工作期間,其電感電流恆大於零,降压变换器即運作在連續模式(continuous mode)下,此模式下的運作原理如圖4所述:

- 當上述的開關導通(圖2的上圖),電感兩側的電壓為,流過電感的電流會線性增加,因為二極體被電壓源V反向導通,理想上二極體不會有電流。

- 當上述的開關斷路(圖2的下圖),二極體被正向導通,電感兩側的電壓為(不考慮二極體壓降),而電感電流會線性下降。

儲存在電感上的能量為

因此在開關導通時,增加,電感能量也會增加,在開關斷路時,減少,電感能量也會降低。電感L就是降压变换器中的儲能元件,將輸入端的能量轉換到輸出端。

的變化率可以表示如下:

其中在導通期間等於,在斷路期間等於。因此在開關導通期間電流的變化為:

其中為一純量,稱為占空比,是0到1之間的數值。

相對的,在開關斷路期間,電流的變化為:

若假設變換器是在穩態下運作,在每一個切換週期T結束時,每個元件的能量都和切換週期T開始時相同。因此表示在時和時的數值相同(圖4)。

因此可以得到下式:

上式也可以用圖形的方式解釋。在圖4中,和黃色的面積成比例,而和橘色的面積成比例。因為上述面積是由電感電壓決定,而這些形狀都是長方形,因此可以求得二形狀的面積,因為穩態,兩者面積會相等。

再配合及。

可以得到

根據此式,可以看出在固定輸入電壓下,輸出電壓和佔空比之間有線性的關係,而是和週期之間的比例,不可能大於1,因此。這就是這種變換器稱為降压变换器的原因。

因此假如要將12V的輸入電壓降壓到3V(輸入電壓的四分之一),在理想電路下,其占空比為25%。

不連續模式(DCM)

[编辑]

有時負載的電流太小,因此在切換週期中,電感的電流有時會下降到0,此情形稱為不連續模式(discontinuous mode),和連續模式之間的差異就是電感會放電直到零電流為止。不過上述的式子會有些變化。

以下仍考慮穩態下的情形,也就是在週期開始和週期結束時,電感的能量相等(在此條件下,會是零)。電感的能量相等可以推得電感電壓VL的平均值為零,也就是黃色區域和橘色區域的面積相等,因此可得:

其中的δ為電感電流下降時間相對週期的比值:

因為送到負載的電流為定值,因此假設其輸出電容夠大,在切換週期中其輸出電壓均為定值,因此可以得到流過電容器的電流平均值為0,電感電流等於輸出電流:

其中為電感電流的平均值。如圖5所示,電感電流波形為三角形,其平均值可以用下式表示:

電感電流在切換週期開始時為0,在開關導通時上昇到ILmax,因此ILmax等於:

替代前一式中的ILmax,可得:

再將δ用輸入電壓Vi、輸出電壓Vo及占空比D來表示,可得:

此式可以改寫為:

在連續模式下,輸出電壓等於占空比乘以輸入電壓。但在不連續模式下,輸出電壓的公式複雜多了,除了和輸入電壓Vi和占空比D有關外,也和電感值L、切換週期T和輸出電流Io有關。

連續模式和不連續模式的邊界

[编辑]

降壓轉換器在負載電流較小時,會運作在不連續模式,負載電流較大時會運作在連續模式。當切換週期結束時,電感電流恰好減少到零電流,此時即為連續模式和不連續模式的邊界。參考圖5的標示,就會是:

因此,在連續模式和不連續模式邊界時的輸出電流(等於電感電流平均值)為:

替代ILmax可得:

在這二個模式的邊界,輸出電壓會同時符合連續模式和不連續模式下的公式,在連續模式下的輸出電壓為

因此Iolim可以寫成下式:

以下定義二個正規化變數:

- 正規化電壓,定義為。若輸出電壓,正規化電壓也會是0,若輸出電壓等於輸入電壓,正規化電壓也是1。

- 正規化電流,定義為。其中的等於電感器在一個週期可以增加的電流最大值,也就是在占空比D=1,電感電流的增加量。因此在變換器穩態運作下,若沒有輸出電流,等於0,若輸出電流為最大輸出電流,則會是1。

配合上述變數,可得:

- 在連續模式下:

- 在不連續模式下:

連續模式和不連續模式邊界的電流值為:

因此,分隔連續模式和不連續模式的曲線為:

此曲線也標示在圖6中,由圖中可以看出在連續模式下,輸出電壓只和輸入電壓和占空比有關,而在不連續模式下的關係就相當複雜了。以控制觀點來看,降压变换器最好可以控制在連續模式下。

非理想電路下的情形

[编辑]

上述的推導都假設是理想電路下的情形:

- 輸出電容器夠大,因此在驅動純電阻負載時其電壓沒有顯著的變化。

- 二極體的順向壓降為0。

- 開關及二極體都沒有切換損失。

上述假設都和實際情形不合,這些元件或電路上的不理想情形會在變換器運作時有負面的影響。

輸出電壓漣波

[编辑]輸出電壓漣波是指輸出電壓在開關導通期間上升,在開關斷路時下降的現象。造成輸出電壓漣波的原因主要包括換頻率、輸出電容、電感、負載及電路中限制電流的元件。若考慮最基本的現象,輸出電壓漣波是因為輸出電容充電及放電造成的:

在開關斷路時,上式的電流為負載電流,開關導通時,上式的電流為電源電流及負載電流之間的差值。時間區間dT是由占空比(duty cycle)和切換頻率決定的。

開關導通時:

開關斷路時:

以量化的角度來看,若輸出電容器或是切換頻率增加,電壓漣波就會下降。輸出電壓漣波是電源供應器的典型設計規格之一,會因許多因素而影響其要求的數值。輸出電容器選用一般會受成本、體積以及不同電容器的不理想特性而影響。切換頻率選擇一般會依效率的要求而決定,一般切換頻率越高,效率越低,而且越可能有電磁干擾(EMI)的問題。

輸出電壓漣波是切換式電流供應器(SMPS)的一大缺點,也是評量SMPS性能的重要指標。

特殊結構

[编辑]同步整流

[编辑]同步降压变换器也是降压变换器的一種,但沒有二極體D,取而代之的是第二個開關S2。在原來的降壓變換器中,二極體只有在開關開路時才是順向偏壓,因此代替二極體的開關S2需有類似特性。在開關S1導通時,開關S2開路,在開關S1開路時,開關S2導通。二個開關不會同時導通。此架構會提昇效率,但也是增加成本,因此需要在這兩者之類有所取捨。

在標準的降压变换器中,二極體D是续流二极管,在開關斷路後一小段時間就會因為二極體二端電壓的上昇而自行導通。二極體壓降產生的功率損失為

其中:

- VD是負載電流為Io時,二極體的電壓降

- D是占空比

- Io是負載電流

若將二極體D用開關S2代替,一般就會選擇低損失的開關,因此就可以提昇變換器的效率。例如RDSON很低的MOSFET就可以用作為開關S2,開關S2功率損失為

上述二種情形下的損失都很明顯和占空比D有關,且飛輪二極體和整流開關(也稱為下方開關)都和開關S1斷路時間佔的比例(1-D)成正比。因此,若系統設計在占空比較低的條件下運作,飛輪二極體或是整流開關的損失會較大,此時若考慮使用同步整流的架構,在效率的改善也會比較明顯。

若沒有實際的數據,讀者很難了解同步整流的好處在哪裡。考慮一個電源供應器,輸入5V,輸出3.3V,額定電流10A。此時的占空比為66%,二極體導通的比率為34%。若使用順向導通壓降為0.7 V的傳統二極體,其導通功率損失為2.38 W,若選用一顆RDSON為0.015 Ω的MOSFET,其導通功率損失就減到0.51 W。因此可以提昇效率,也減少了電源供應器的發熱。

另一個同步整流变换器的好處是它在本質上是雙向的,因此也允許功率由輸出端流到輸入端,適用於需要再生制動的場合。若功率反向流動,其運作方式會比較像升壓變換器。

同步整流变换器有優點,不過也有其缺點。下方開關一般會比飛輪二極體要貴,而且因為需要有二組輸出,而且是互補式(一個導通,另一個斷路)的開關驅動電路,其複雜性就提高很多。

同步整流变换器的驅動器需要避免上下二個開關同時導通,這種故障稱為直通(shootthrough),這會讓輸入電壓的二端直接短路,產生大電流。最簡單的避免方法是讓開關 S1先斷路,等待一小段時間,再將S2導通。不過這段時間要夠長,可以確保開關 S1和S2不會同時導通,這個就會產生額外的損失。另一個作法是非重疊式(non-overlap)保護,就是在開關S1、S2和L在電路上相連接的部份根據偵測到的電壓判斷其狀態,若電壓高於或低於一定值,就啟動時間延遲的機制。

多相降压变换器

[编辑]

多相降压变换器是在輸入和負載之間有多個基本的降压变换器並聯而成。在切換週期內,各相的降压变换器會在不同的時間導通及關閉,各相的降压变换器多半都會用到同步整流的技術。

因為各相切換的時間錯開,n相降压变换器對負載的反應速度會是基本降压变换器的n倍,但又不會有n倍切換頻率會產生的切換損失,因此可以針對快速變化的負載(例如現在的CPU)調整占空比。

降压变换器在切換漣波上也會有明顯的下降,一方式是因為輸出端看到的等效切換頻率(切換頻率的n倍)提高[3],而且假如占空比的n倍恰好是整數,其切換漣波會變為0。在某幾相電感電流的增加量恰好和另外幾相電感電流的下降量抵消,因此沒有切換漣波。

另一個好處是在n相降压变换器中,負載電流由n個降压变换器分開處理,這也表示開關的熱可以分散在較大的區域,散熱會比較方便。

此電路架構已用在電腦的主機板中,將開關電源提供的12 VDC電壓轉換到較低(例如1V),符合CPU需求的電壓。現在的CPU功率需求可能會超過200W[4],功率變化非常的快,而且漣波電壓需小於10mV。典型主機板的電源會用三相或四相的降压变换器。

多相降压变换器隱含的主要問題是如何確保各相的電流是平衡分配的。電流的平衡可以用幾個方式達到。可以用「無損失」(losslessly)的方式量測各相電流,方式是量測各相電感器或是下方開關(整流開關)的跨壓(在下方開關導通時)。此方式稱為「無損失」的原因是它主要是靠電感器的串聯雜散電阻(或是下方開關的導通電阻),不需額外加入電阻。各一個方式是在電路中串聯電阻,量測跨壓,此方式更準確,也比較容易調整,不過在體積、效率及成本上都比較不利。

電流也可以由輸入側來量測,可以透過各相的上方開關進行「無損失」量測,也可以在輸入端直接串聯一個電阻量測。後者的挑戰性較高,因為切換損失不容易濾掉,但價值會比各相加一個電阻要便宜。

影響效率的因素

[编辑]導通損失(和負載有關):

- 電晶體或是MOSFET在導通時的電阻。

- 二極體順向電降(若是肖特基二极管,約為0.4 V到0.7 V)。

- 電感繞組的電阻

- 電容器的等效串聯電阻

切換損失:

- 電壓-電流重疊的損失

- 切換頻率*CV2的損失

- 反向延遲損失

- 因為驅動MOSFET閘及控制器本身耗能產生的損失。

- 電晶體漏電流損失,以及控制器待機功耗[5]。

阻抗匹配

[编辑]降压变换器可以用來作阻抗匹配,以符合最大功率传输定理。像光伏系統中用的最大功率點追蹤(MPPT)就可配合降压变换器。

根據電功率的公式::

其中

- Vo為輸出電壓

- Io為輸出電流

- η為效率(數值在0到1之間)

- Vi為輸入電壓

- Ii為輸入電流

根據歐姆定律:

其中

- Zo為輸出阻抗

- Zi為輸入阻抗

用這些式子取代功率公式中的Io及Ii可得:

假設降压变换器在連續模式下(IL > 0):A

其中:

- D為占空比

將此式代入前式的Vo中,可得:

可以簡化為:

最後可得:

因此可以透過調整占空比來調整阻抗。這可以用在一些阻抗需要動態調整的應用中。

參考資料

[编辑]- ^ Mammano, Robert. "Switching power supply topology voltage mode vs. current mode." Elektron Journal-South African Institute of Electrical Engineers 18.6 (2001): 25-27.

- ^ Keeping, Steven. Understanding the Advantages and Disadvantages of Linear Regulators. DigiKey. 2012-05-08 [2016-09-11]. (原始内容存档于2016-09-23).

- ^ Guy Séguier, Électronique de puissance, 7th edition, Dunod, Paris 1999 (in French)

- ^ Tom's Hardware: "Idle/Peak Power Consumption Analysis". [2016-09-12]. (原始内容存档于2019-08-14).

- ^ iitb.ac.in - Buck converter (PDF). (原始内容 (PDF)存档于2011-07-16). 090424 ee.iitb.ac.in

- P. Julián, A. Oliva, P. Mandolesi, and H. Chiacchiarini, "Output discrete feedback control of a DC-DC Buck converter," in Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE’97), Guimaraes, Portugal, 7-11Julio 1997, pp. 925–930.

- H. Chiacchiarini, P. Mandolesi, A. Oliva, and P. Julián, "Nonlinear analog controller for a buck converter: Theory and experimental results", Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE’99), Bled, Slovenia, 12–16 July 1999, pp. 601–606.

- M. B. D’Amico, A. Oliva, E. E. Paolini y N. Guerin, "Bifurcation control of a buck converter in discontinuous conduction mode", Proceedings of the 1st IFAC Conference on Analysis and Control of Chaotic Systems (CHAOS’06), pp. 399–404, Reims (Francia), 28 al 30 de junio de 2006.

- Oliva, A.R., H. Chiacchiarini y G. Bortolotto "Developing of a state feedback controller for the synchronous buck converter", Latin American Applied Research, Volumen 35, Nro 2, Abril 2005, pp. 83–88. ISSN 0327-0793.

- D’Amico, M. B., Guerin, N., Oliva, A.R., Paolini, E.E. Dinámica de un convertidor buck con controlador PI digital. Revista Iberoamericana de automática e informática industrial (RIAI), Vol 4, No 3, julio 2007, pp. 126–131. ISSN 1697-7912.

- Chierchie, F. Paolini, E.E. Discrete-time modeling and control of a synchronous buck converter .Argentine School of Micro-Nanoelectronics, Technology and Applications, 2009. EAMTA 2009.1–2 October 2009, pp. 5 – 10 . ISBN 978-1-4244-4835-7 .

相關條目

[编辑]- Boost變換器

- Buck-boost變換器

- Split-pi 變換器(Boost-buck變換器)

- 通用的直流-直流轉換器及开关电源

外部連結

[编辑]- Interactive Power Electronics Seminar (iPES) Many Java applets demonstrating the operation of converters

- Model based control of digital buck converter (页面存档备份,存于互联网档案馆) Description and working VisSim source code diagram for low cost digital control of DC-DC buck converters

- SPICE simulation of the buck converter (页面存档备份,存于互联网档案馆)

- Tutorial video explaining buck converters with example buck converter circuit design Portuguese Web Archive的存檔,存档日期2016-05-16

- Switch-Mode Power Supply Tutorial - Detailed article on DC-DC converters which gives a more formal and detailed analysis of the Buck including the effects of non-ideal switching (but, note that the diagram of the buck-boost converter fails to account for the inversion of the polarity of the voltage between input and output).

- DC-DC Power Converter Case study

- On the Power Efficiency Optimization (页面存档备份,存于互联网档案馆)